Ein asynchrones Signal wie RTTY lebt davon, dass man sich bei jedem Start-Bit neu auf die Phase synchronisiert, anstatt starr durchzulaufen.

Der Standard-Symbol-Sync-Block ist ein “Clock Recovery”-Block, der versucht, eine kontinuierliche Uhr beizubehalten. Bei RTTY mit 1,5 Stopp-Bits (einer ungeraden Länge) ist ein starrer Takt oft problematisch, da das Stop-Bit ggf länger als der Takt ist.

Bei einer Übertragung mit 50Baud liegt der Takt bei 20ms, ein Stop-Bit mit einer Länge von 1.5 ist aber 30ms lang. Wie bereits im vorherigen Artikel erwähnt entstehen dadurch ggf zusätzliche Bits oder es fallen welche weg.

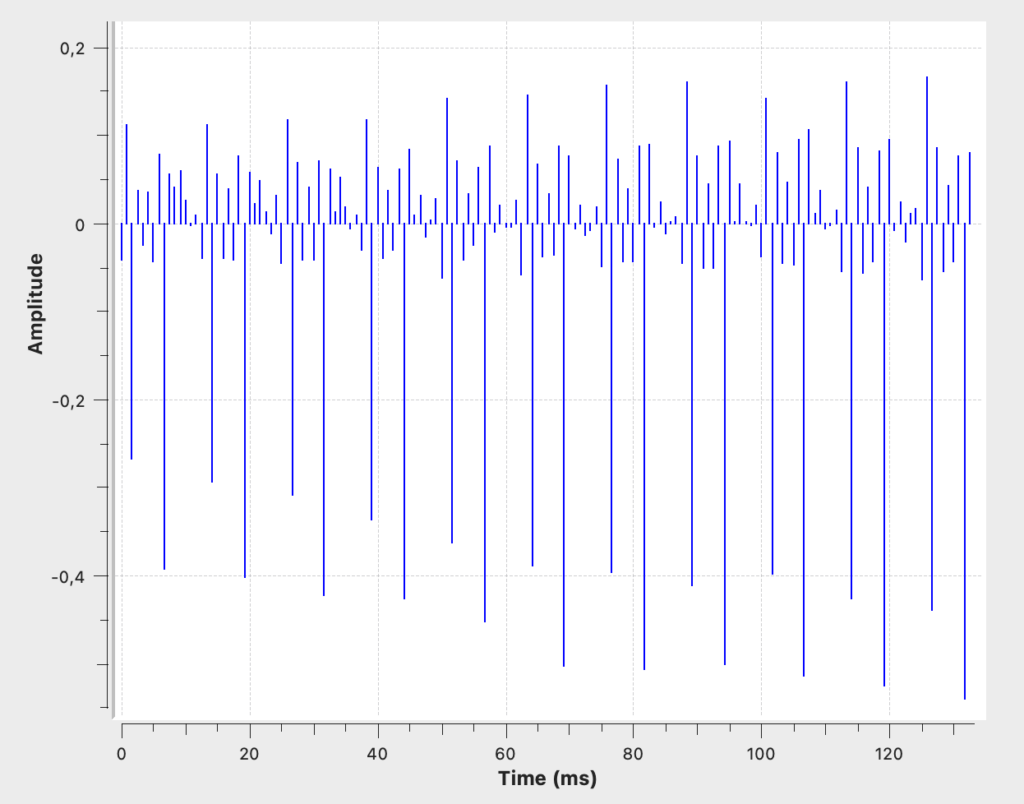

Der Error Ausgang des Blocks liefert die entsprechenden Abweichungen.

Die regelmäßigen Spikes alle 20 ms (entspricht 50 Baud) zeigen wann der TED einen Fehler erkennt.

Die Spikes gehen hier fast ausschließlich nach unten (negativ). Das bedeutet, der Block erkennt dass sein interner Takt “zu früh” dran ist im Vergleich zur realen Flanke. Er muss also ständig “bremsen”.

Nach jeweils 5 Datenbits verändert sich der Rhythmus oder es gibt eine Pause in der Fehlermeldung.

Das halbe Stopbit bringt den Sync Block also aus dem Tritt,

Die Idee ist nun, dem Syncblock die doppelte Baudrate vorzugeben. Das halbe Bit wird nun zu einem Ganzen und die Dauer eines Bits ist damit konstant.

<strong>Original (50 Baud):</strong>

┌─────┬────┬────┬────┬────┬────┬──────────┐

│Start│ D0 │ D1 │ D2 │ D3 │ D4 │ Stop │

│ 1 │ 5 Bits │ 1.5 Bits │

└─────┴────┴────┴────┴────┴────┴──────────┘

Total: 7.5 Bits @ 20ms/Bit = 150ms

<strong>Mit doppelter Rate (100 Baud):</strong>

┌──┬──┬──┬──┬──┬──┬──┬──┬──┬──┬──┬──┬──┬──┬──┐

│St│D0│D0│D1│D1│D2│D2│D3│D3│D4│D4│Sp│Sp│Sp│??│

│1 │ 10 Half-Bits │ 3 Half-Bits │

└──┴──┴──┴──┴──┴──┴──┴──┴──┴──┴──┴──┴──┴──┴──┘

Total: 15 Half-Bits @ 10ms/Half-Bit = 150msCode-Sprache: HTML, XML (xml)

Vorteil der Lösung:

- Symbol Sync arbeitet mit ganzen Zahlen und kann unverändert laufen.

- Es gibt keine Drift über längere Nachrichten hinweg

- Jedes Bit wird 2 mal gesampled worduch die Rauschrobustheit verbessert wird.

- Das Stopbit kann validiert werden, wodurch Framing Fehler erkannt werden können. Mindestens 2 von 3 der Stopbits /Marks müssen 1 sein.

Nachteil

- Die Bandbreite verdoppelt sich effektiv, was jedoch aufgrund der CutOff Frequenzen des Tiefpasssfilters keine wesentliche Beeinträchtigung darstellt.

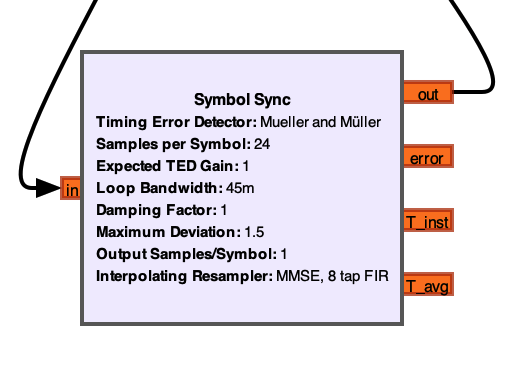

Hier noch einmal die benötigten Einstellungen der Blöcke:

| Samplerate | 12000 | ergibt sich auch aus der im Wave File genutzten Rate |

| Baud | 100 | Die doppelte Geschwindigkeit wird benutzt |

| Shift | 225 | bleibt unverändert, der Hub von 450Hz ändert sich nicht. |

Quadartur Demodulation

| gain | -8.488 | -12000/(2*pi*112.5) |

Lowpass Filter

| CuttOff Frequenz | 100Hz | aufgrund der doppelten Baudrate muss der Filter breiter sein |

| Width | 50Hz | |

| Decimation | 10 | Die Samplerate kann nach der Filterung reduziert werden |

Symbol Sync Block

| SPS | 12 | berechnet sich aus Samplerate / Decimation des vorherigen TP-Filters / 100 Baud |

| loop_bw | 0.01 | |

| Output Samples per Symbol | 1 | Es wird 1 Sample pro Bit ausgegeben |

| Als Algorithmus wird Müller & Muller verwendet |

Das Ergebnis:

In der ursprünglichen Auswertung waren einige Zeichenfehler vorhanden, die nun verschwunden sind.

CQ CQ CQ DE DDK2 DDH7 DDK9

FREQUENCIES 4583 KHZ 7646 KHZ 10100.8 KHZ

RYRYRYRYRYRYRYRYRYRYRYRYRYRYRYRYRYRYRYRYRYRYRY<mark style="background-color:rgba(0, 0, 0, 0)" class="has-inline-color has-luminous-vivid-orange-color"><strong><FE></strong></mark>RYCode-Sprache: JavaScript (javascript)<FE> ist dabei kein Zeichenfehler sonder zeigt, dass an dieser Stelle ein Framing Fehler aufgetreten ist. Ein Framing Error tritt auf, wenn der Decoder nach den 5 Datenbits eine 1 erwartet, aber eine 0 vorfindet. Da nun aber 3 Half-Bits (1,5 Stopp-Bits) vorliegen, erkennt der Decoder sofort, wenn er durch den asynchronen Versatz “zu früh” in das nächste Start-Bit rutscht.

Majority Vote Logik:

Durch die doppelte Baudrate verfügen wir nu über 2 Abtastwerte pro Bit.

[0,0] ist dabei ein eindeutiges Space Bit

[1,1] ein eindeutiges Mark Bit

[0,1] und [1,0] ist ein Unentschieden.

Im Code wird ein Datenbit als 1 gewertet, sobald eine 1 vorhanden ist. Das macht den Decoder ggf. für Rauschen anfälliger. Für die Ermittlung der Datenbits können wir diese Toleranz beibehalten. Für das Startbit werden aber zwei Einsen erforderlich